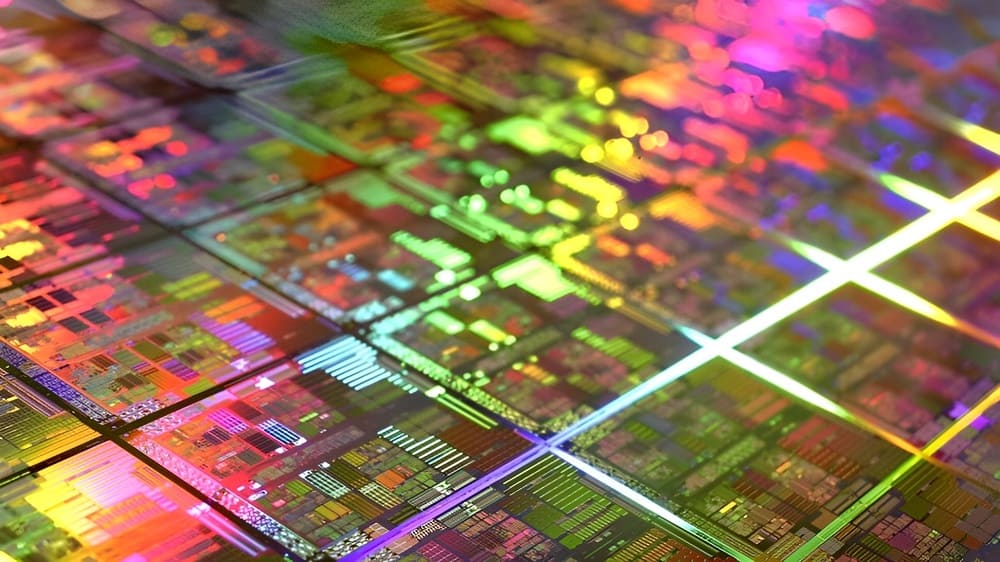

گزارش intel و tsmc درباره پیشرفت cfet ترانزیستور نسل بعدی

به گزارش

eeNewsEurope، اینتل و TSMC قرار است پیشرفت خود را در مورد ترانزیستورهای اثر میدان مکمل (CFETs) در کنفرانس بینالمللی دستگاههای الکترونیکی (IEDM) رونمایی کنند. CFETها قرار است در دهه آینده جانشین ترانزیستورهای گیت همه جانبه (GAA) شوند. مفهوم CFET ها که شامل لایه بندی ترانزیستورهای نوع n و p بر روی یکدیگر است، ابتدا توسط موسسه تحقیقاتی IMEC در سال 2018 معرفی شد. در حالی که بیشتر مطالعات اولیه از محافل آکادمیک سرچشمه میگیرد، شرکتهای تجاری مانند اینتل و TSMC اکنون به این عرصه ورود کردهاند و فعالانه در حال بررسی این نوع ترانزیستور نسل بعدی هستند.

اینتل

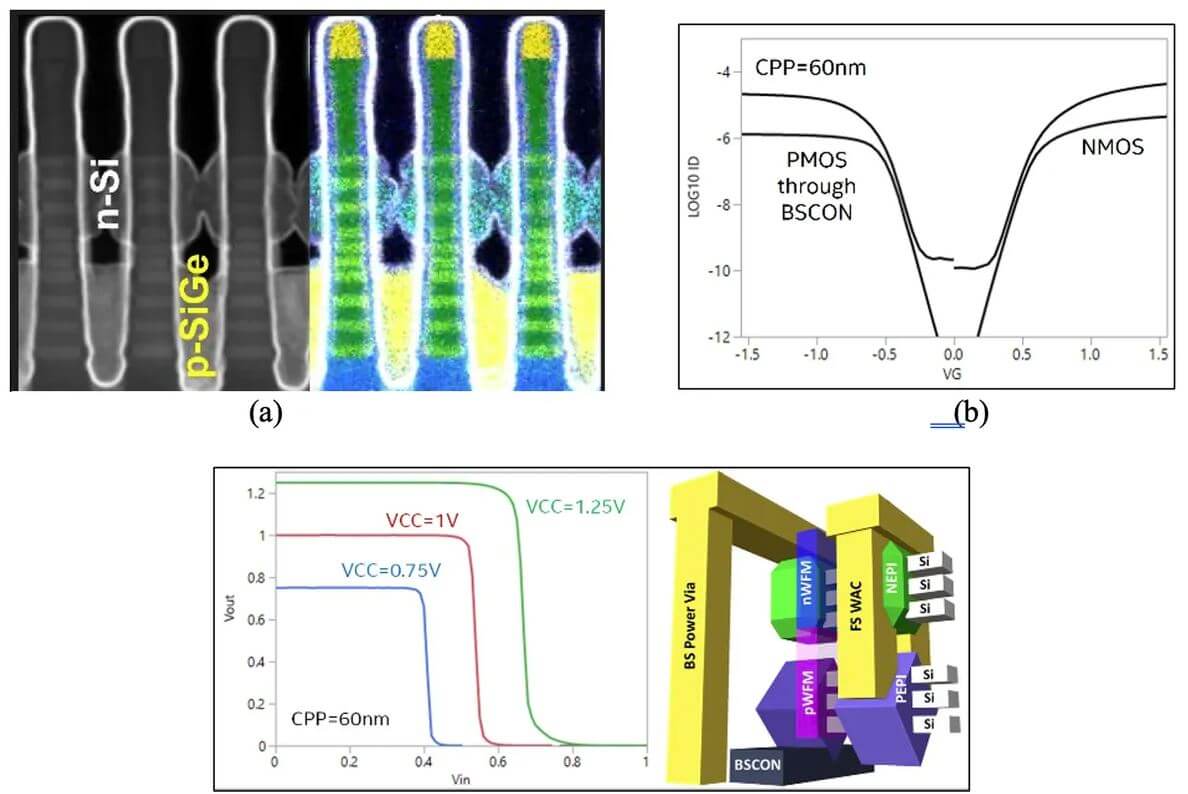

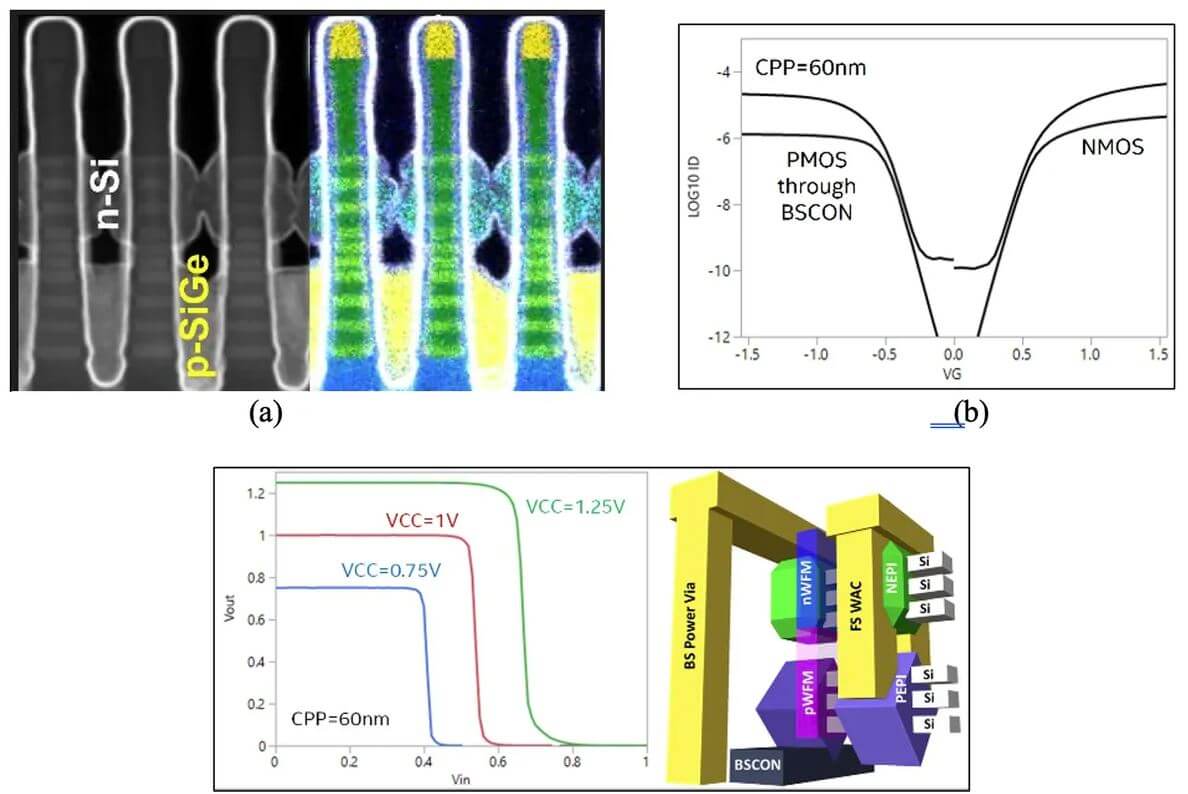

محققان اینتل یک CFET سه بعدی یکپارچه ساختهاند که سه نانوروبان n-FET را در بالای سه نانوروبان p-FET ترکیب میکند و یک شکاف عمودی 30 نانومتری را حفظ میکند. ارائه اینتل با عنوان "نمایش یک اینورتر CMOS انباشته در پیچ گیت 60 نانومتری از طریق برق و تماس مستقیم دستگاه پشتی" مدارهای تست اینورتر عملکردی را با استفاده از CFET در گیت 60 نانومتری توصیف می کند. این طرح همچنین دارای

اپیتاکسی دو منبع تخلیه با لایه عمودی و پشته های دروازه فلزی دوقلو است، و همچنین از انتقال برق پشتی PowerVia شرکت استفاده می کند.

TSMC

برای اینکه از رقیب خود عقب نماند، TSMC روش عملی CFET خود را که برای فناوری منطقی طراحی شده و دارای گیت 48 نانومتری است، مورد بحث قرار خواهد داد. طراحی کارخانه ریختهگری بر ترانزیستورهای نانو ورق لایهای نوع n که بر روی همتایان نوع p قرار گرفتهاند، با نسبت جریان روشن / خاموش قابلتوجهی که شش مرتبه بزرگی را در بر میگیرد، برجسته میشود. به گفته این شرکت، ترانزیستورهای TSMC دوام خود را با بیش از 90 درصد تست موفقیت آمیز ثابت کرده اند. در حالی که شرکت اعتراف می کند که ویژگی های بیشتری برای استفاده کامل از قابلیت های فناوری CFET وجود دارد، کار در حال انجام، نشان دهنده گامی اساسی به سوی این هدف است.

ترانزیستور نسل بعدی

CFET ها تغییر قابل توجهی را در طراحی ترانزیستور ایجاد می کنند، با روی هم قرار گرفتن عمودی آنها به دو ترانزیستور اجازه می دهد تا در ردپای یک ترانزیستور قرار گیرند و در نتیجه تراکم ترانزیستور را بر روی یک تراشه افزایش می دهد. این طراحی نه تنها راه را برای افزایش بهره وری فضا هموار می کند، بلکه یک طرح مدار منطقی CMOS ساده تر را ترویج می کند و کارایی طراحی را تسهیل می کند. علاوه بر این، ساختار ذاتی CFET ها ممکن است منجر به کاهش اثرات پارازیتی شود و پیشرفت های بالقوه ای در عملکرد و بهره وری توان ارائه دهد. قابلیتهای طراحی قابل تطبیق آنها، مانند توانایی متعادل کردن تغییرات کانالهای NMOS و PMOS، همراه با نوآوریهایی مانند تحویل برق در پشت، فرآیند تولید را سادهتر کرده و CFETها را به یک توسعه امیدوارکننده در حوزه فناوری ترانزیستور تبدیل میکند. تلاش های اینتل و TSMC اهمیت فناوری CFET را برای آینده صنعت نیمه هادی ها برجسته می کند.

مجله صفرویک

مجله صفرویک